Package reliability and qualification continues to evolve with the electronics industry. New electronics applications require new approaches to reliability and qualification. In the past, reliability meant discovering, characterizing and modeling failure mechanisms and determining their impact on the reliability of the circuit. Today, reliability can involve tradeoffs between performance and reliability, assessing the impact of new materials, dealing with limited margins, etc. in particular, the proliferation of new package types. This requires information on subjects like: statistics, testing, technology, processing, materials science, chemistry, and customer expectations. While customers expect high reliability levels, incorrect testing, calculations, and qualification procedures can severely impact reliability. Your company needs competent engineers and scientists to help solve these problems. Semiconductor Reliability and Product Qualification is an online course that offers detailed instruction on a variety of subjects pertaining to semiconductor reliability and qualification. This course is designed for every manager, engineer, and technician concerned with reliability in the semiconductor field, qualifying semiconductor components, or supplying tools to the industry.

Package reliability and qualification continues to evolve with the

electronics industry. New electronics applications require new

approaches to reliability and qualification. In the past, reliability

meant discovering, characterizing and modeling failure mechanisms and

determining their impact on the reliability of the circuit. Today,

reliability can involve tradeoffs between performance and reliability,

assessing the impact of new materials, dealing with limited margins, the

proliferation of new package types, etc. This requires information on

subjects like: statistics, testing, technology, processing, materials

science, chemistry, and customer expectations. While customers expect

high reliability levels, incorrect assumptions, testing, calculations,

and qualification procedures can severely impact reliability. Your

company needs competent engineers and scientists to help solve these

problems.

Package reliability and qualification continues to evolve with the

electronics industry. New electronics applications require new

approaches to reliability and qualification. In the past, reliability

meant discovering, characterizing and modeling failure mechanisms and

determining their impact on the reliability of the circuit. Today,

reliability can involve tradeoffs between performance and reliability,

assessing the impact of new materials, dealing with limited margins, the

proliferation of new package types, etc. This requires information on

subjects like: statistics, testing, technology, processing, materials

science, chemistry, and customer expectations. While customers expect

high reliability levels, incorrect assumptions, testing, calculations,

and qualification procedures can severely impact reliability. Your

company needs competent engineers and scientists to help solve these

problems.

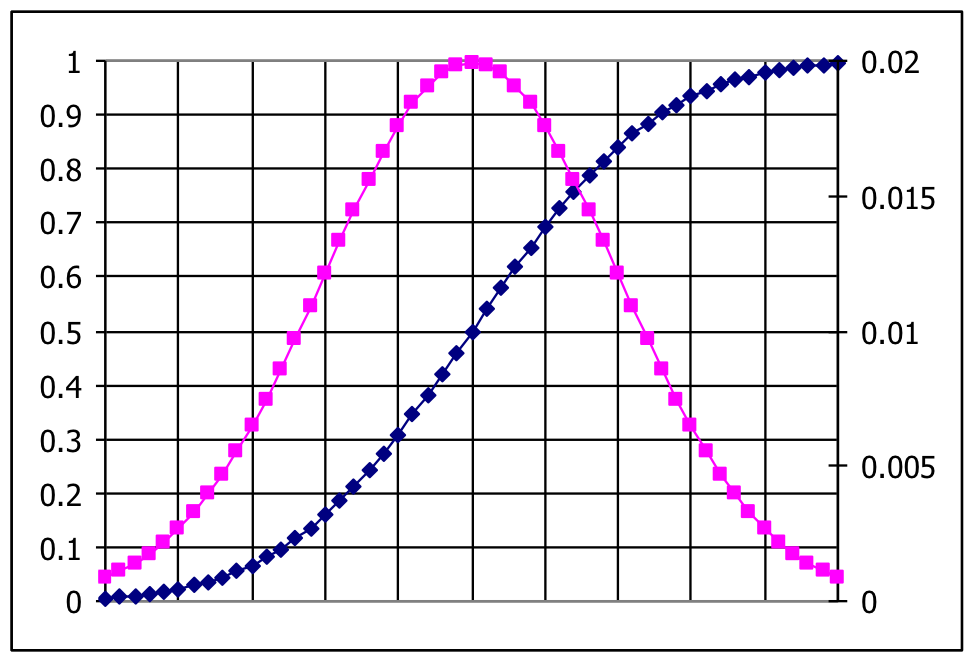

In order to

successfully qualify new products, the product engineer needs to

understand the basics of reliability. He or she needs to understand

what we mean by reliability, and the basic equations used to calculate

reliability. He or she also needs to understand how we calculate

reliability values using statistics and distributions, and how the

sample size, and acceleration factors into the calculations. We discuss

the four main distribution types: Exponential, Weibull, Normal, and

Lognormal. We discuss how to take the results of an accelerated stress

test and transform it into data that can be used to help predict

reliability related to a failure mechanism.

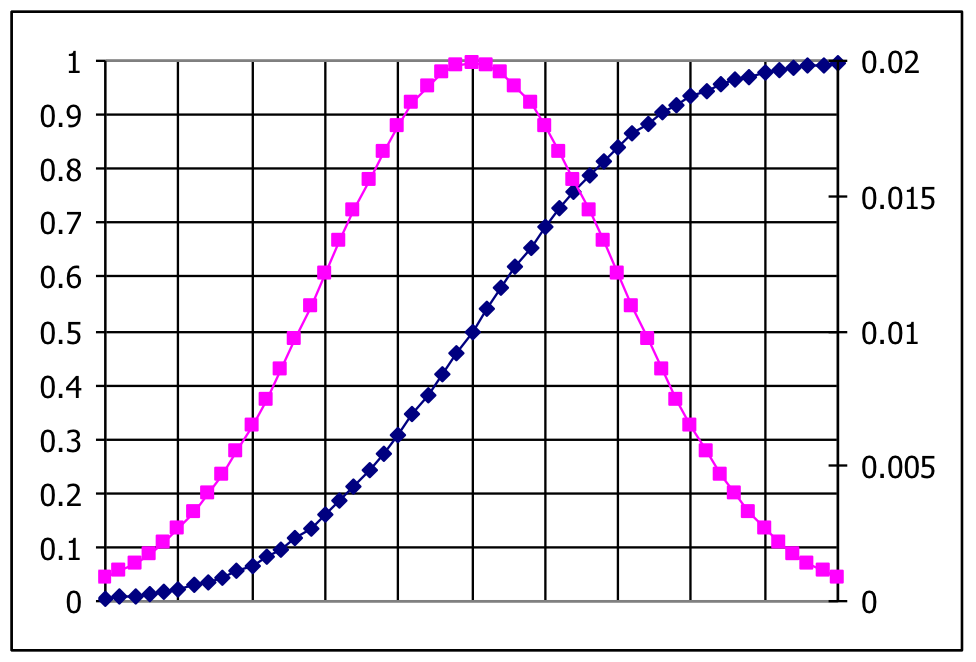

In order to

successfully qualify new products, the product engineer needs to

understand the basics of reliability. He or she needs to understand

what we mean by reliability, and the basic equations used to calculate

reliability. He or she also needs to understand how we calculate

reliability values using statistics and distributions, and how the

sample size, and acceleration factors into the calculations. We discuss

the four main distribution types: Exponential, Weibull, Normal, and

Lognormal. We discuss how to take the results of an accelerated stress

test and transform it into data that can be used to help predict

reliability related to a failure mechanism.

In

order to determine the overall reliability of the product, the product

engineer needs to understand the basic failure mechanisms that can

affect the semiconductor device. In this segment we cover both the die

and package level failure mechanisms. At the die level they include:

Time Dependent Dielectric Breakdown (TDDB), Hot Carrier Injection (HCI),

Negative Bias Temperature Instability (NBTI), Positive Bias Temperature

Instability (PBTI), Electromigration (EM), Stress Voiding or Stress

Migration, and Mobile Ions. At the package level they include:

Moisture and Corrosion, Thermo-Mechanical Stress, and Thermal

Degradation

In

order to determine the overall reliability of the product, the product

engineer needs to understand the basic failure mechanisms that can

affect the semiconductor device. In this segment we cover both the die

and package level failure mechanisms. At the die level they include:

Time Dependent Dielectric Breakdown (TDDB), Hot Carrier Injection (HCI),

Negative Bias Temperature Instability (NBTI), Positive Bias Temperature

Instability (PBTI), Electromigration (EM), Stress Voiding or Stress

Migration, and Mobile Ions. At the package level they include:

Moisture and Corrosion, Thermo-Mechanical Stress, and Thermal

Degradation

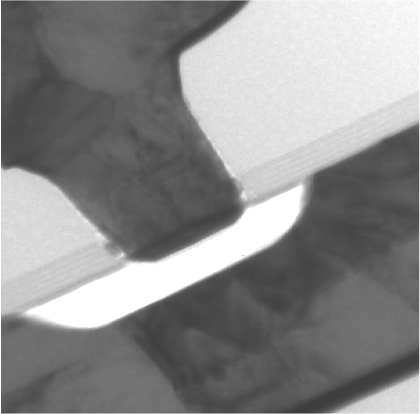

In addition

to reliability issues with the chip itself, the product engineer needs

to be aware of reliability issues that can occur when the chip is placed

in the customer's application. This means we need to understand how

the interaction of the package and the customer's printed circuit board

(PCB) affects the overall reliability. A big part of this interaction

is solder joint reliability. This interaction also involves underfills,

and the chip substrate (in some instances). Another part of system

reliability is understanding how the chip will interact in the system

when it is subjected to electrical stress. We discuss Electrical

Overstress (EOS), Electrostatic Discharge (ESD), Latch-up, and

Snapback. We also discuss radiation effects and how they can cause

system failures.

In addition

to reliability issues with the chip itself, the product engineer needs

to be aware of reliability issues that can occur when the chip is placed

in the customer's application. This means we need to understand how

the interaction of the package and the customer's printed circuit board

(PCB) affects the overall reliability. A big part of this interaction

is solder joint reliability. This interaction also involves underfills,

and the chip substrate (in some instances). Another part of system

reliability is understanding how the chip will interact in the system

when it is subjected to electrical stress. We discuss Electrical

Overstress (EOS), Electrostatic Discharge (ESD), Latch-up, and

Snapback. We also discuss radiation effects and how they can cause

system failures.

The

final segment of the Product Qualification process are the

qualification tests themselves. In this section we'll discuss the basic

concepts behind the Product Qualification tests. This includes Wafer

Level Reliability Testing (the test structures and the test equipment)

and the Package Level tests. We then discuss the major Qualification

processes, including the military approach in MIL-STD 883, the JEDEC

approach in JEDEC Standard 47 (JESD-47), and the automotive approach in

AEC-Q100. Finally, we discuss the JEDEC tests themselves and what they

are designed to look for.

The

final segment of the Product Qualification process are the

qualification tests themselves. In this section we'll discuss the basic

concepts behind the Product Qualification tests. This includes Wafer

Level Reliability Testing (the test structures and the test equipment)

and the Package Level tests. We then discuss the major Qualification

processes, including the military approach in MIL-STD 883, the JEDEC

approach in JEDEC Standard 47 (JESD-47), and the automotive approach in

AEC-Q100. Finally, we discuss the JEDEC tests themselves and what they

are designed to look for.